### Nanoelectronics on Si

#### Prof. J. Raynien Kwo 郭瑞年

Physics Department National Tsing Hua University

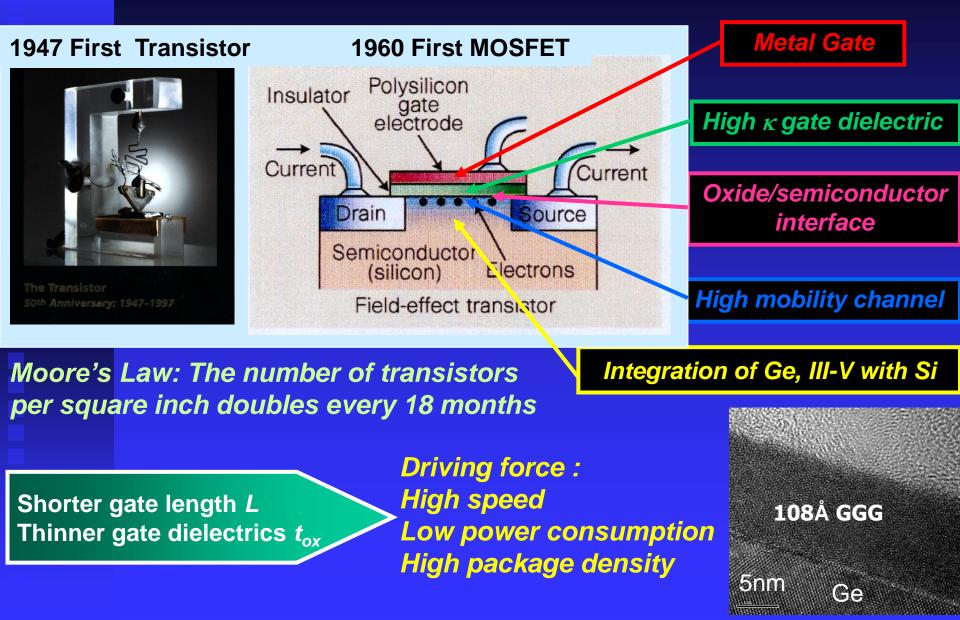

- 縮小尺度至100 nm以內的科技:

Top-down之奈米結構的雕刻細化

莫爾定律(Moore's law-每1.5年縮小30%

尺寸)

- 操控原子(分子)的科技:Bottom-up之 奈米體系的成長組裝 費曼的主張一從底部作起,下面還有無限 寬廣的空間

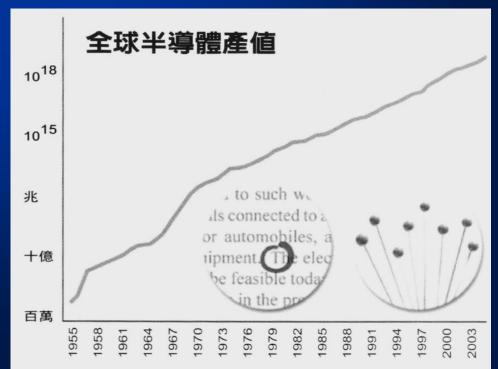

### 近來大力推動奈米科技的背景

### 來自微電子學可能遭遇瓶頸的考慮 Moore's Law: 摩爾定律 A 30% decrease in the size of

printed dimensions every 1.5 years. 矽晶上電子原件數每1年半會增加一倍

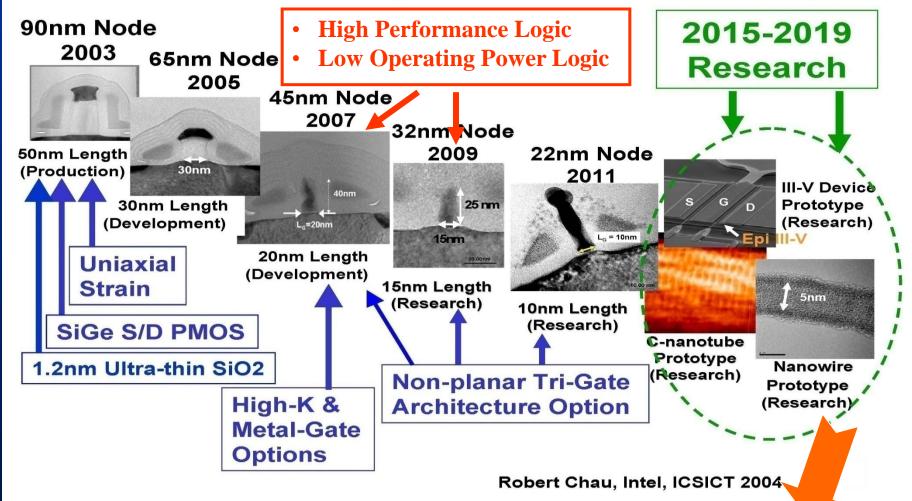

### Si CMOS Device Scaling – Beyond 22 nm node High κ, Metal gates, and High mobility channel

### **Intel Transistor Scaling and Research Roadmap**

#### **Transistor Scaling and Research Roadmap**

#### More non-silicon elements introduced

### Scaling Limits to CMOS Technology

Shrinking the junction depth increasing the carrier concentration

**Reliability:** 25 22 18 16 Å processing and yield issue

**Tunneling :** 15 Å

Design Issue: chosen for  $1A/cm^2$  leakage  $I_{on}/I_{off} >> 1$  at 12 Å

#### **Bonding:**

Fundamental Issues---

- how many atoms do we need to get bulk-like properties?

EELS -- Minimal 4 atomic layers !!

- Is the interface electronically abrupt?

- Can we control roughness?

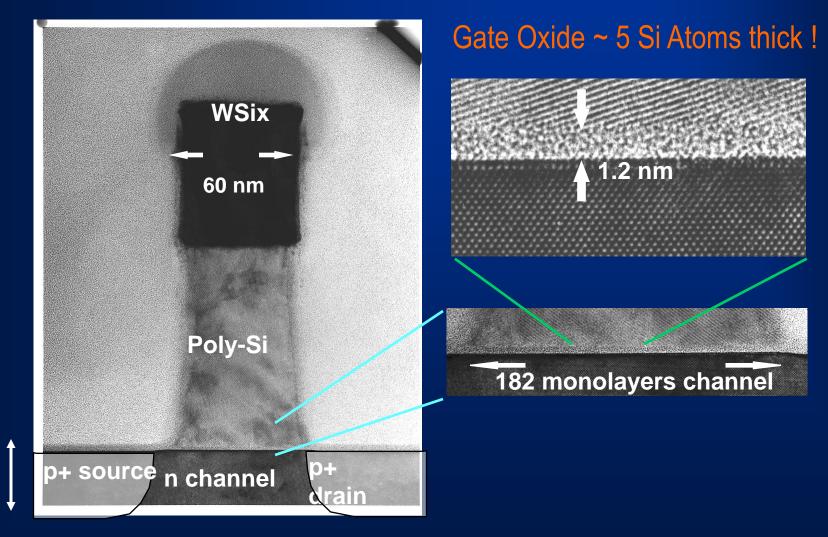

In 1997, a gate oxide was 25 silicon atoms thick.

In 2007, a gate oxide will be 5 silicon atoms thick, if we still use  $SiO_2$

> and a 2 of t atoms be at interf

and at least 2 of those 5 atoms will be at the interfaces.

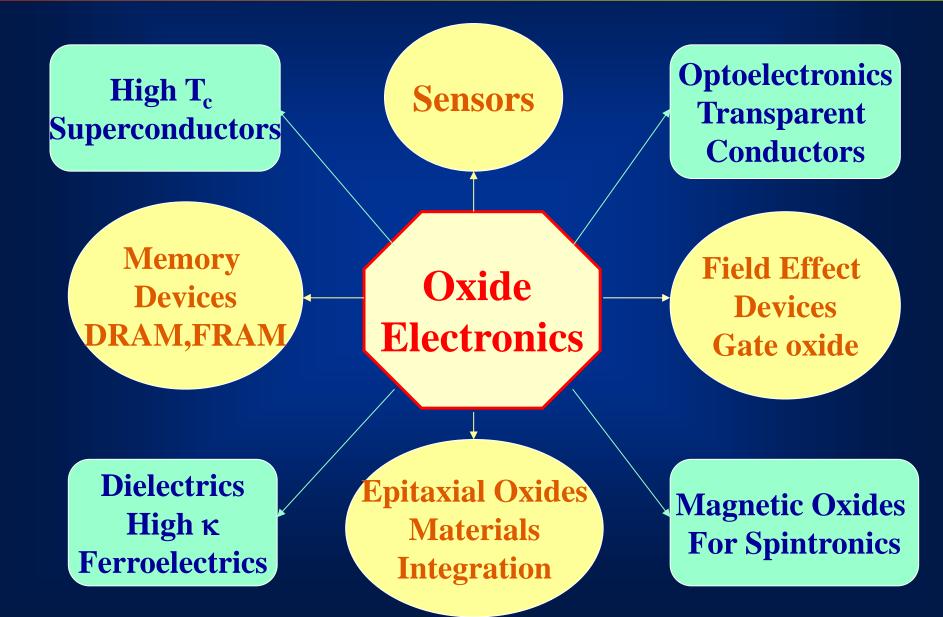

#### The Development of Oxide Electronics in Two Decades

The alternative high k gate dielectrics replacing SiO<sub>2</sub> for 33 nm Si CMOS by year 2009, and 22 nm for year 2011.

-- Materials requirements

-- Processing integration issues

MBE grown HfO<sub>2</sub> high k gate dielectrics

-- thermal stability studies by MEIS and TEM

-- electrical performance

Integration of ALD + MBE template approach

### Fundamental Materials Selection Guidelines

$Si + MO_{x} \longrightarrow M + SiO_{2}$   $Si + MO_{x} \longrightarrow MSi_{2} + SiO_{2}$   $Si + MO_{x} \longrightarrow MSiO_{x} + SiO_{2}$

Thermodynamic stability in contact with Si to 750°C and higher. (Hubbard and Schlom) Alkaline earth oxide, IIIB, IVB oxide and rare earth oxide

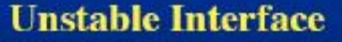

- Dielectric constant, band gap, and conduction band offset

- Defect related leakage,

- substantially less than SiO<sub>2</sub> at  $t_{eq} < 1.5$  nm

- Low interfacial state density  $D_{it} < 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$

- Low oxygen diffusivity

- Crystallization temperature >1000°C

- $t_{eq}$ : equivalent oxide thickness (EOT) to be under 1.0 nm  $t_{eq} = t_{ox} \kappa_{SiO2} / \kappa_{ox}$

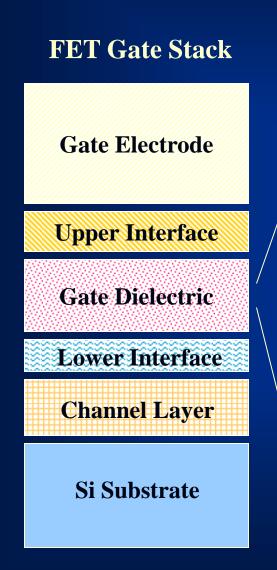

### Integration Issues for High K Gate Stack

### **Critical Integration Issues**

- Morphology dependence of leakage *Amorphous vs crystalline films?*

- Interfacial structures

- Thermal stability

- Gate electrode compatibility

- Reliability

#### **Fundamental Limitations**

- Fixed charge

- Dopant depletion in poly-Si gate

- Dopant diffusion

- Increasing field in the channel region

### **Basic Characteristics of Binary Oxide Dielectrics**

| Dielectrics                                                                                                               | SiO <sub>2</sub> | Al <sub>2</sub> O <sub>3</sub> | Y <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub> | $Ta_2O_5$  | ZrO <sub>2</sub>  | La <sub>2</sub> O <sub>3</sub> | TiO <sub>2</sub>  |

|---------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|-------------------------------|------------------|------------|-------------------|--------------------------------|-------------------|

| Dielectric constant                                                                                                       | 3.9              | 9.0                            | 18                            | 20               | 25         | 27                | 30                             | 80                |

| Band gap (eV)<br>Band offset (eV)                                                                                         | 9.0<br>3.2       | 8.8<br>2.5                     | 5.5<br>2.3                    | 5.7<br>1.5       | 4.5<br>1.0 | 7.8<br>1.4        | 4.3<br>2.3                     | 3.0<br>1.2        |

| Free energy of formation<br>MO <sub>x</sub> +Si <sub>2</sub> → M+ SiO <sub>2</sub><br>@727C, Kcal/mole of MO <sub>x</sub> | -                | 63.4                           | 116.8                         | 47.6             | -52.5      | 42.3              | 98.5                           | 7.5               |

| Stability of amorphous phase                                                                                              | High             | High                           | High                          | Low              | Low        | Low               | High                           | High              |

| Silicide formation ?                                                                                                      | -                | Yes                            | Yes                           | Yes              | Yes        | Yes               | Yes                            | Yes               |

| Hydroxide formation ?                                                                                                     | -                | Some                           | Yes                           | Some             | Some       | Some              | Yes                            | Some              |

| Oxygen diffusivity<br>@950C (cm <sup>2</sup> /sec)                                                                        | $2x \ 10^{-14}$  | 5x 10 <sup>-25</sup>           | ?                             | 5                | 5          | 10 <sup>-12</sup> | 5                              | 10 <sup>-13</sup> |

### Assessing Thermodynamic Stability

Gate Dielectric Material Silicon

3nm

Ideal "Gedanken" Interface

#### Stable Interface

rd\_O

Ta2Os(7.5nm)

SiOx(2nm)

Si Substrate

TEM by Don J. Werder G.B. Alers et al., Appl Phys. Lett. 73 (1998) 1517.

E-Si

3 nm

TEM by David A. Muller J. Kwo et al., J. Appl. Phys. 89 (2001) 3920.

### **Band Offsets of Dielectrics with Si**

J. Roberson, JVST 18, 1785, (2000)

World production in year 2003: 1 x 10<sup>19</sup> transistors World population: 6.4 x 10<sup>9</sup> people So, the world produces:

- ~  $1.5 \times 10^9$  transistors/person each year

- ~  $1.2 \times 10^8$  transistors/person each month

- ~ 4M transistors/person each day

- ~ 3K transistors/person each minute

- ~ 50 transistors/person per second

And Taiwan produces ~5000 transistors/person/per second

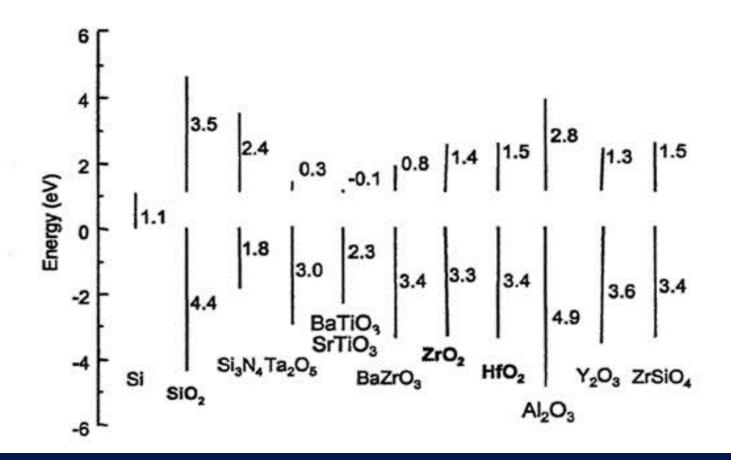

#### MBE Integrated Multi-chamber System For Nano Electronics

Now located in the Nano Technology Center, ITRI, Hsin Chu, Taiwan since 7/2003.

### Multi-chamber MBE with in-situ ALD, XPS, SPM System

### High κ Dielectrics for Si

#### Epitaxial crystalline films on Si

- (A) Cubic CaF<sub>2</sub> structure:

- (111) orientation is more common than (100)

- e.g. Ca  $F_2$  (111), CeO<sub>2</sub> (111) on Si(111) with  $\varepsilon \sim 26$ YSZ (100) on Si(100) with  $\varepsilon \sim 25-30$

- (B) Cubic  $Mn_2O_3$  structure

- ~ 8 unit cells of incomplete fluorite structure

- e.g.  $Y_2O_3$  (110) on Si(100) with  $\varepsilon \sim 16-18$ Gd<sub>2</sub>O<sub>3</sub> (110) on Si(100) with  $\varepsilon \sim 12-14$

- (C) Ternary perovskite structure

- e.g.  $SrTiO_3(100)$  on Si(100) with  $\epsilon \sim 70-80$  (Oakridge, Motorola) using a Sr silcide <sup>1</sup>/<sub>4</sub> monolayer for epi-growth

#### Amorphous oxide films on Si

- e.g.  $Si_3N_4$ ,  $Al_2O_3$ ,  $Ta_2O_5$ , ZrTiSnOx,  $TiO_2$  Interfacial layer present

- Amorphous  $Gd_2O_3$  and  $Y_2O_3$  films

- Amorphous  $SiO_2$  added with Hf or Zr . (G. Wilks et al)

### **Research Programs**

$\blacktriangleright$ Low defect high  $\kappa$  ultrathin films --Interface engineering --Electrical characterization and optimization ► Identify new material candidates for metal gate --Metal gate/high k integration  $\blacktriangleright$  Integration of high  $\kappa$ , and metal gate with Si- Ge strained layer Integration of high  $\kappa$ , and metal gate with strained Si

High k dielectrics for high mobility III-V semiconductors

### **MBE Growth of High κ Oxides**

- Ultrahigh vacuum, multi-chamber MBE system.

- Electron-beam evaporation of oxide sources from pressed ceramic pellets.

- 2 inch RCA-cleaned Si wafers, hydrogen passivated, followed by prompt insertion into UHV.

- In-situ heating to 400-500C to attain a (2 x 1) reconstructed Si surface.

- Substrate temperature of 550C for epitaxial films.

- Room temperature deposition for amorphous films.

- Maintain low pressure during growth < 1.0 x 10<sup>-9</sup> torr.

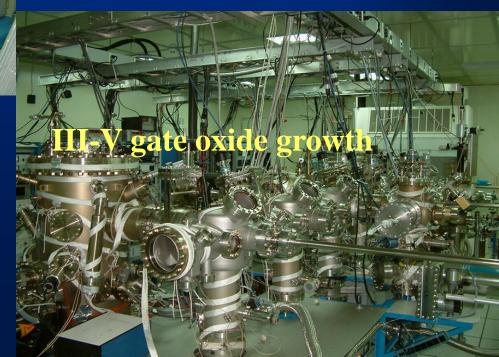

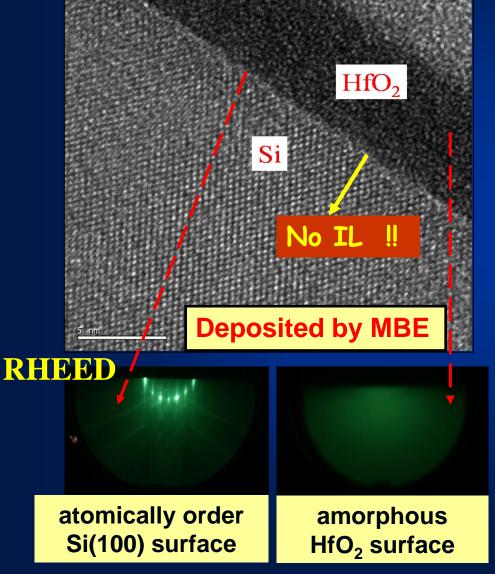

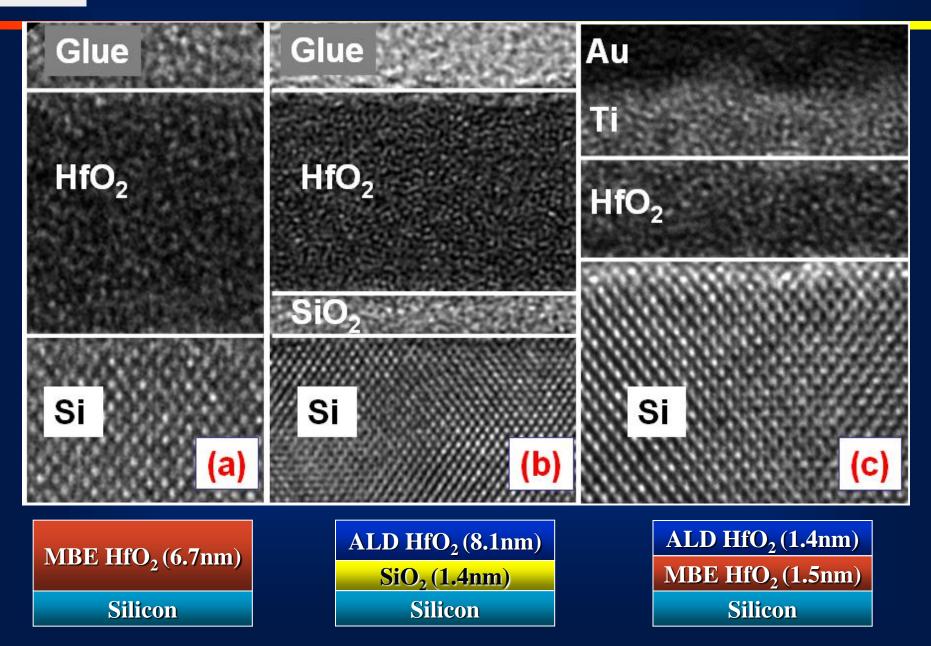

Amorphous  $HfO_2$  film 6.0 nm  $SiO_2$  and Hf silica is nearly absent !

atomically order Si(100) surface

# The Technique of Medium Energy Ion Scattering (MEIS)

- MEIS is a refinement of the more common technique of Rutherford backscattering spectrometry (RBS), but with enhanced depth and angle resolution.

- In a typical MEIS experiment, a collimated beam of mono energetic (typically 100 keV) light ions (H+ or He+) impinges onto a target along a known direction.

- The energy and angle of the scattered ions are analyzed simultaneously and allow MEIS to measure atomic mass, depth, and surface structure from the following physical principles;.

**Mass** - ions scattered from the surface of a material undergo energy loss by a 'billiard ball' type collision with surface atoms. The scattered ion energy thus relates directly to the mass of the scattering atom. This effect can be seen in Figure where the signal from O, Si and Ge are separated in energy

**Depth** - ions scattered from below the surface lose energy inelastically at a rate proportional to the ion's path length in the target. This extra energy loss thus relates directly to the depth of the scattering atom. In favorable cases MEIS can achieve a depth resolution of one atomic layer.

**Surface structure** - when the ion beam is aligned with a crystallographic axis the surface atoms shadow deeper atoms from the ion beam. This alignment therefore makes the technique surface specific and, for a particular crystal, certain ingoing directions can allow the ion beam to illuminate only the top one, two, or three layers according to choice. Ions scattered from the second layer will have their outward paths blocked at certain angles by first layer atoms. The variation in scattered ion intensity with angle thus relates to the geometrical arrangement of surface atoms.

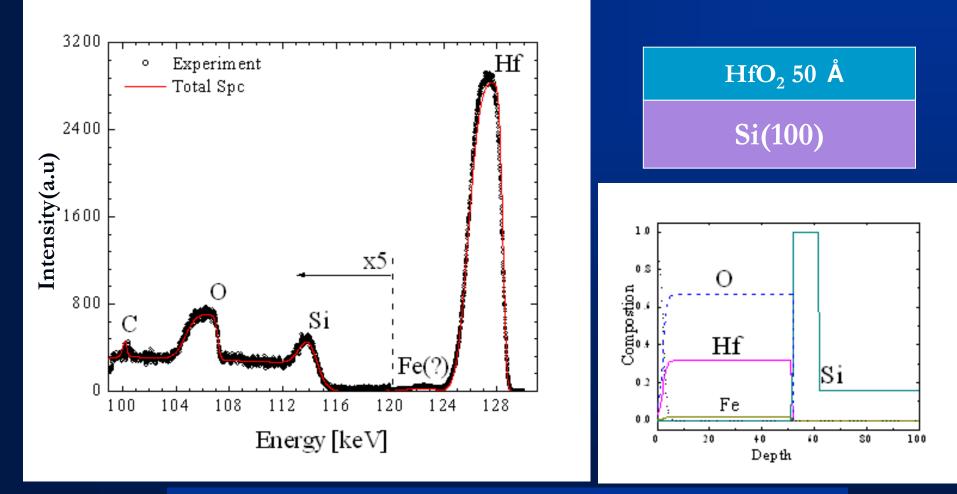

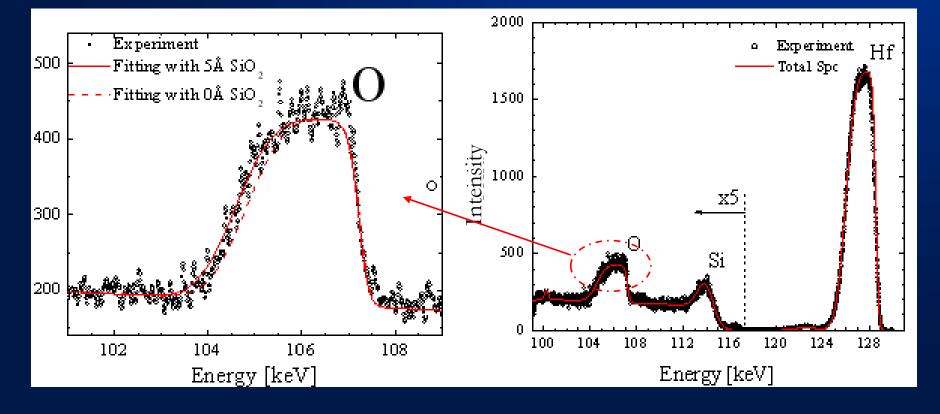

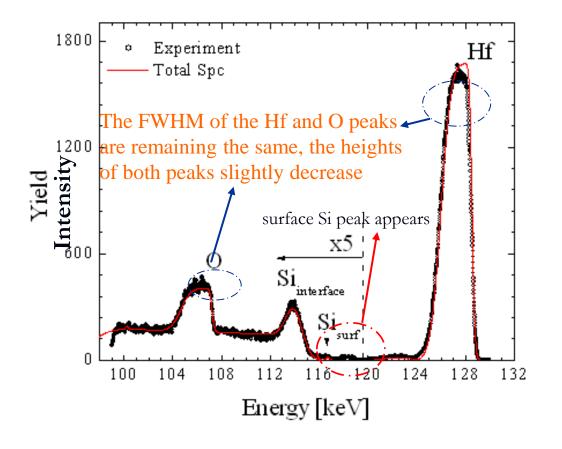

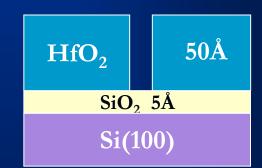

### Medium Energy Ion Scattering (MEIS) Study of the High κ Dielectric / Si Interface and Stability

With Rutgers University using 130 keV proton beam It shows the absence of silica near the interface.

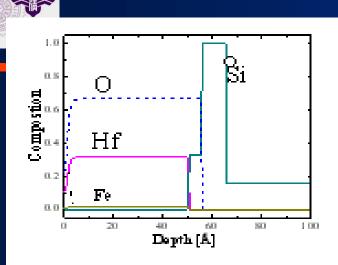

### Vacuum annealing at 630°C

Broadening of the O peak and small increase in the Si peak indicate some interfacial  $SiO_2$  formation about 0.4 nm.

### Annealing from 630°C to 950°C

#### A possible structure after high temperature anneal

Discontinuities and islands were formed in  $HfO_2$ .

#### MEIS with Rutgers University

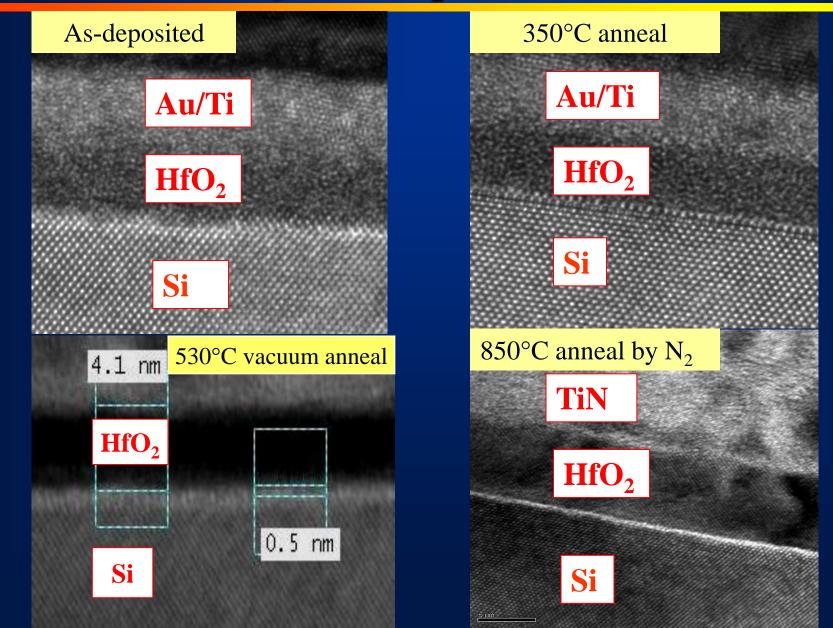

### HRTEM Study of Thermal Stability of High κ HfO<sub>2</sub> Gate Stacks

- Thermal stability of thin films

- $\succ HfO_2 \longrightarrow Lowering the dopant activation temperature to 700°C$

- > TiN  $\rightarrow$  Using Ti/TiN bilayer structure

- Process integration

- ➤ 4 inch Si (LOCOS)→2 inch Si (MBE)

$\rightarrow$  Successful integration

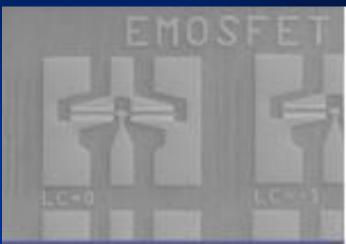

### $TiN/HfO_2/Si$ High $\kappa$ MOSFET

- A self-sligned process

- With LOCOS isolation

- $\succ$  HfO<sub>2</sub> gate dielectrics

- TiN metal gate

- 2 inch MBE-grown high κ films

- ➤ A 4 inch Si line in ERSO for isolation

- A 6 inch Si line in NDL for processing

- W / L ~ 100 μm/ 1.5 μm

- EOT ~ 26 A ( $t_{ox} = 10 \text{ nm}$ )

- $I_d \sim 8.5 \text{ mA } @ V_{gs} = 4V$

- Gm = 48.5 mS/mm

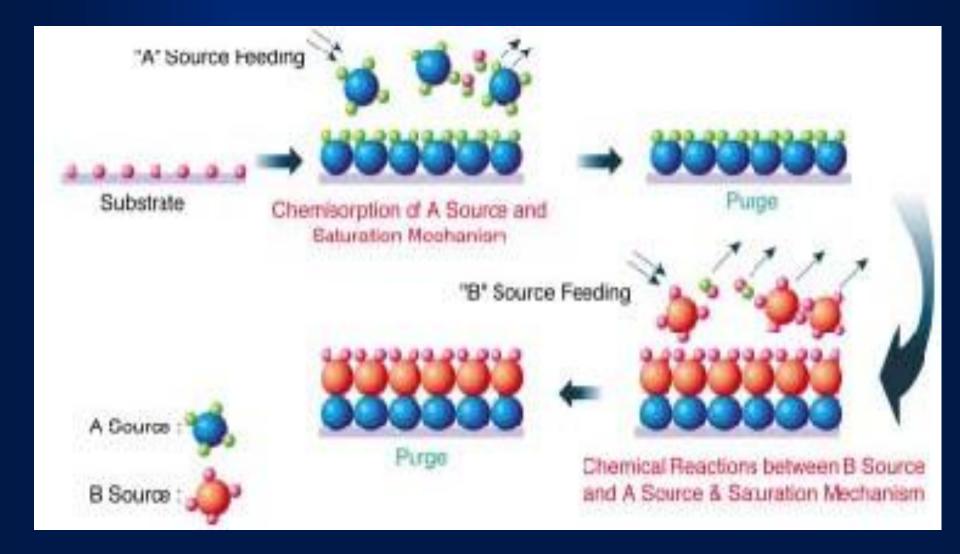

### Atomic Layer Deposition (ALD)

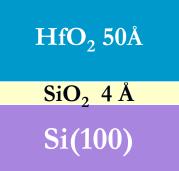

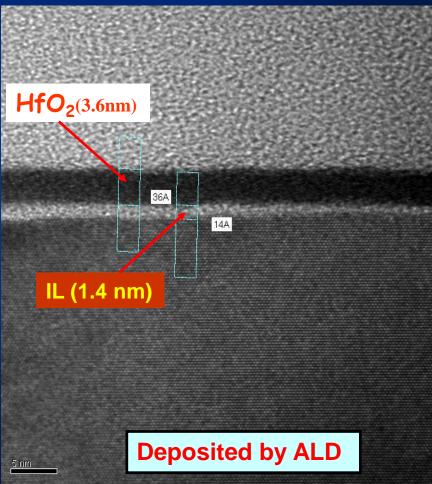

#### Growth Mechanism : Formation of interfacial SiO<sub>2</sub> is hard to avoid.

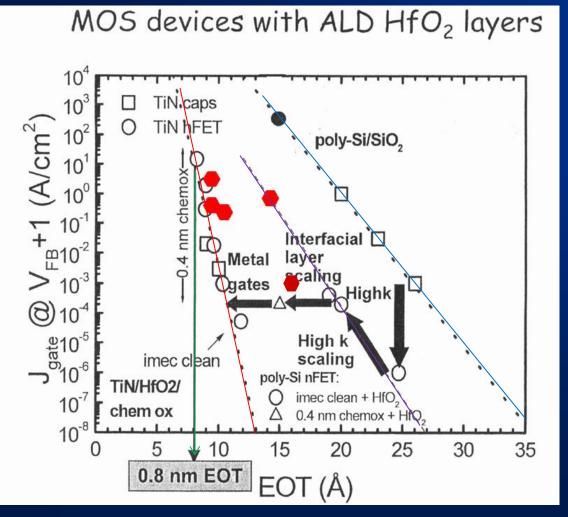

### Comparison between the MBE and ALD films

M. Houssa in Symposium D, MRS Spring Meeting, April 12-16, 2004. MBE-grown

Au/HfO<sub>2</sub>/Si MOS diodes

are denoted in red hexagons

★ HfO<sub>2</sub> film 4.4 nm thick, with J<sub>L</sub> ~  $10^{-3}$  A/cm<sup>2</sup>, κ of 21, and EOT of 0.9 nm

\*  $t_{eq} = EOT$ Equivalent Oxide Thickness  $t_{eq} = t_{ox} \kappa_{SiO2} / \kappa_{ox}$

## Can you make an excellent HfO<sub>2</sub> Film with a low EOT ?

Interface Engineering !

### Structural properties of MBE-grown HfO<sub>2</sub>

#### **HRTEM**

#### **HRTEM**

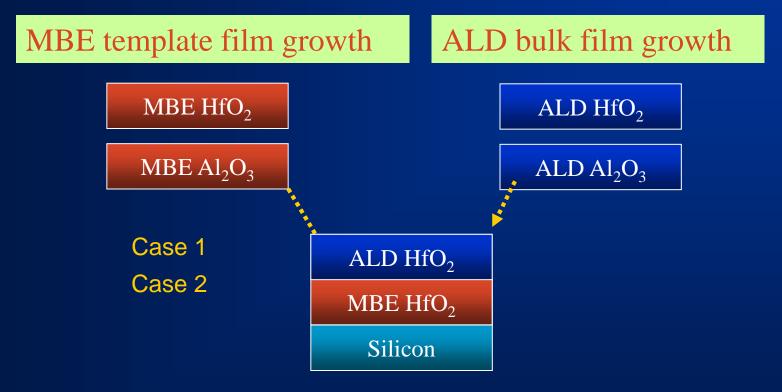

### The MBE Template for ALD Growth

#### MBE and ALD composite film deposition procedure

• Low pressure ( <1x 10<sup>-8</sup> torr ) maintained during MBE growth • ALD precursors : TMA, H<sub>2</sub>O, T<sub>substrate</sub> : 300 $^{\circ}$ C

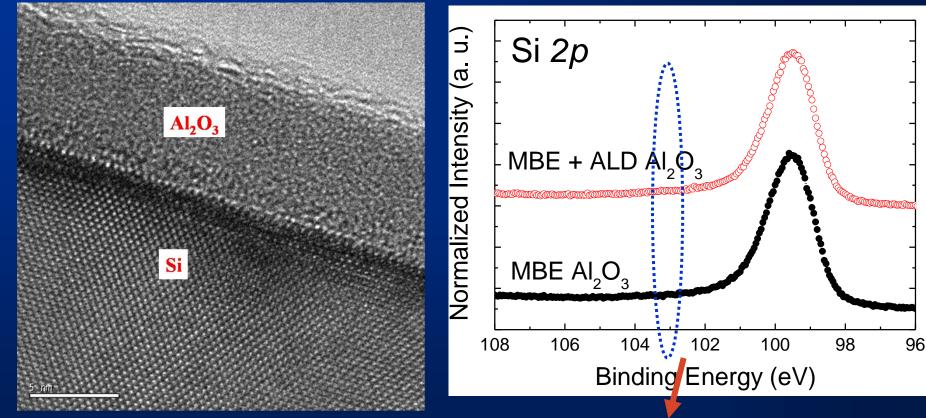

### The structure of ALD Al<sub>2</sub>O<sub>3</sub> with a MBE Al<sub>2</sub>O<sub>3</sub> template

#### ΓΕΜ

#### AR-XPS

No peak formed at 103.4eV

No SiO<sub>2</sub> formed at interface for both MBE and MBE+ALD Al<sub>2</sub>O<sub>3</sub>

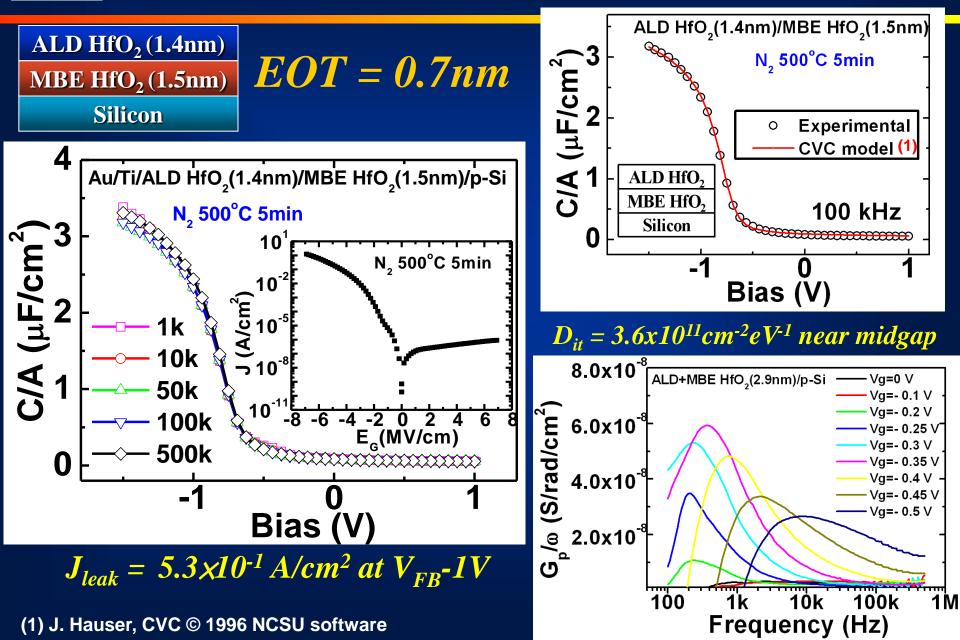

For  $HfO_2$ , have achieved EOT= 0.7 nm

#### Free structure of ALD HfO<sub>2</sub> with a MBE HfO<sub>2</sub> template

#### Reference electrical characteristics of ALD/MBE HfO<sub>2</sub> (2.9nm)

|                        | Our work (TiN//p-Si)             |                                  |             |                                                       |                                                             |                                                             |                          |  |  |  |

|------------------------|----------------------------------|----------------------------------|-------------|-------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|--------------------------|--|--|--|

| Dielectrics            | MBE-<br>HfO <sub>2</sub><br>10nm | ALD-<br>HfO <sub>2</sub><br>10nm | YDH<br>10nm | ALD-HfO <sub>2</sub> 8nm+<br>MBE-HfO <sub>2</sub> 2nm | ALD-HfO <sub>2</sub> 4nm+<br>MBE-HfO <sub>2</sub> 2nm       | YDH 7nm+<br>Y <sub>2</sub> O <sub>3</sub> 1nm               | ALD-<br>HfO₂             |  |  |  |

| L <sub>g</sub> (µm)    | 1.5                              | 1.5                              | 1.5         | 1                                                     | 1                                                           | 1                                                           | 0.08                     |  |  |  |

| EOT(nm)                | 2.5                              | 3                                | 1.5         | 2.5                                                   | 1.5                                                         | 1.6                                                         | 1                        |  |  |  |

| G <sub>m</sub> (mS/mm) | 35                               | 55                               | 70          | 120@V <sub>G</sub> =3.5V<br>100@V <sub>G</sub> =2.5V  | <u>100@V<sub>G</sub>=2.5V</u><br>1250 <sup>#</sup><br>1875* | <u>125@V<sub>G</sub>=2.5V</u><br>1560 <sup>#</sup><br>2500* | 132<br>1650              |  |  |  |

| l <sub>d</sub> (mA/mm) | 80                               | 55                               | 118         | 240@V <sub>G</sub> =4V<br>70@V <sub>G</sub> =2.5V     | <u>155@V<sub>o</sub>=2.5V</u><br>1940 <sup>#</sup><br>2910* | <u>195@V<sub>o</sub>=2.5V</u><br>2440 <sup>#</sup><br>3900* | 140 <sup>1</sup><br>1750 |  |  |  |

# After normaliztion to gate length of 0.08 µm

\* After normaliztion to gate length of 0.08 µm and EOT of 1 nm

<sup>1</sup> R. Chau, et al, IEEE Electron Device Letters **25**, No. 6, 408 (2004)

First demonstration of atomically abrupt high k HfO<sub>2</sub>/Si interface.

- Successful integration of the 6 inch Si CMOSFET processing in NDL with our 2" MBE high  $\kappa$  dielectric films using a TiN metal gate to produce a gate length 1.5 µm transistor device.

Novel ALD + MBE template approach, superior electrical performance.